GPMC_FCLK

GPMC_CLK

nBE1/nBE0

nCS

nADV

nOE

DIR

WAIT

Valid Address

Valid Address

Data 0

Data 0

OUT

IN

OUT

CSONTIME

CSRDOFFTIME

ADVONTIME

ADVRDOFFTIME

OEONTIME

OEOFFTIME

RDACCESSTIME

RDCYCLETIME

A[27:17]

A[16:1]/D[15:0]

www.ti.com

GPMC

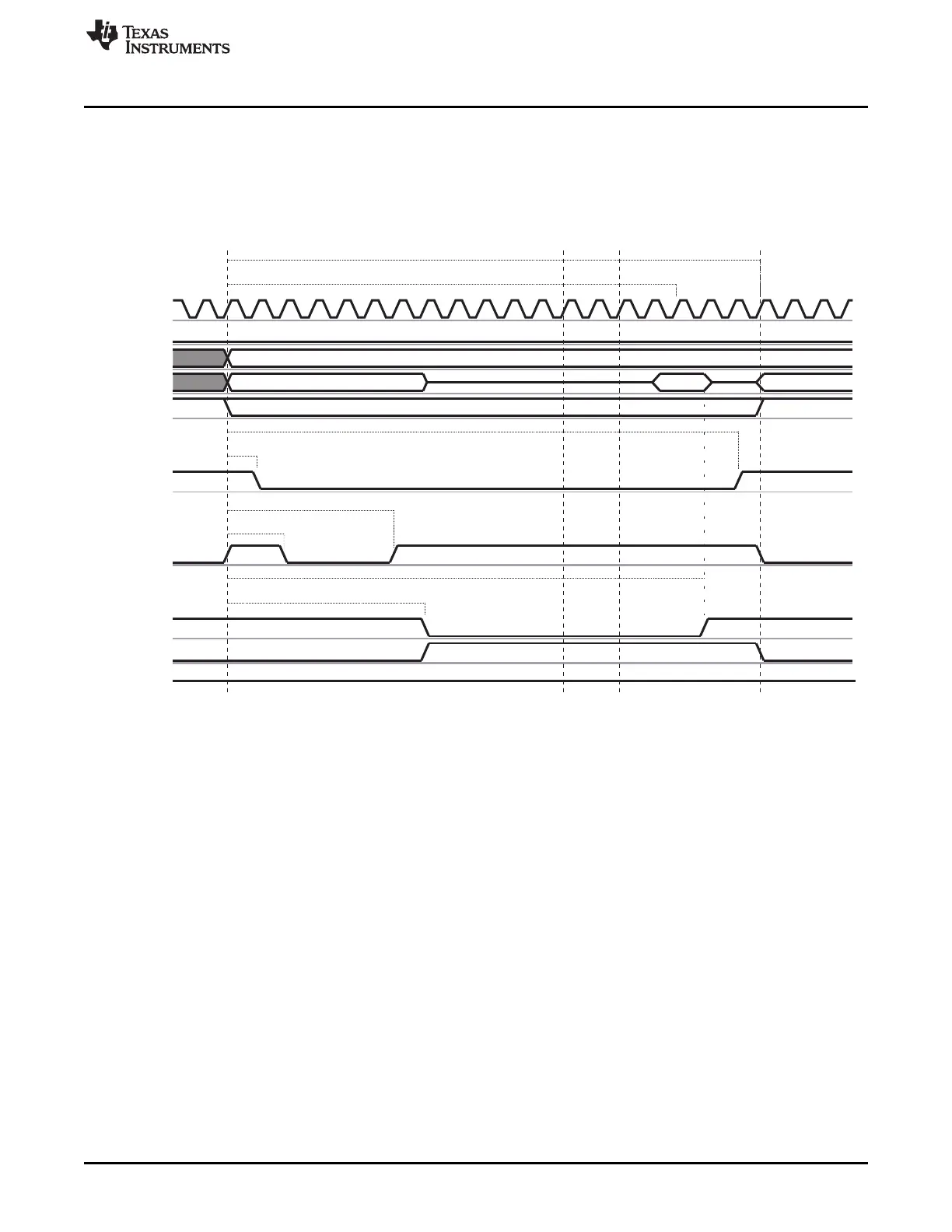

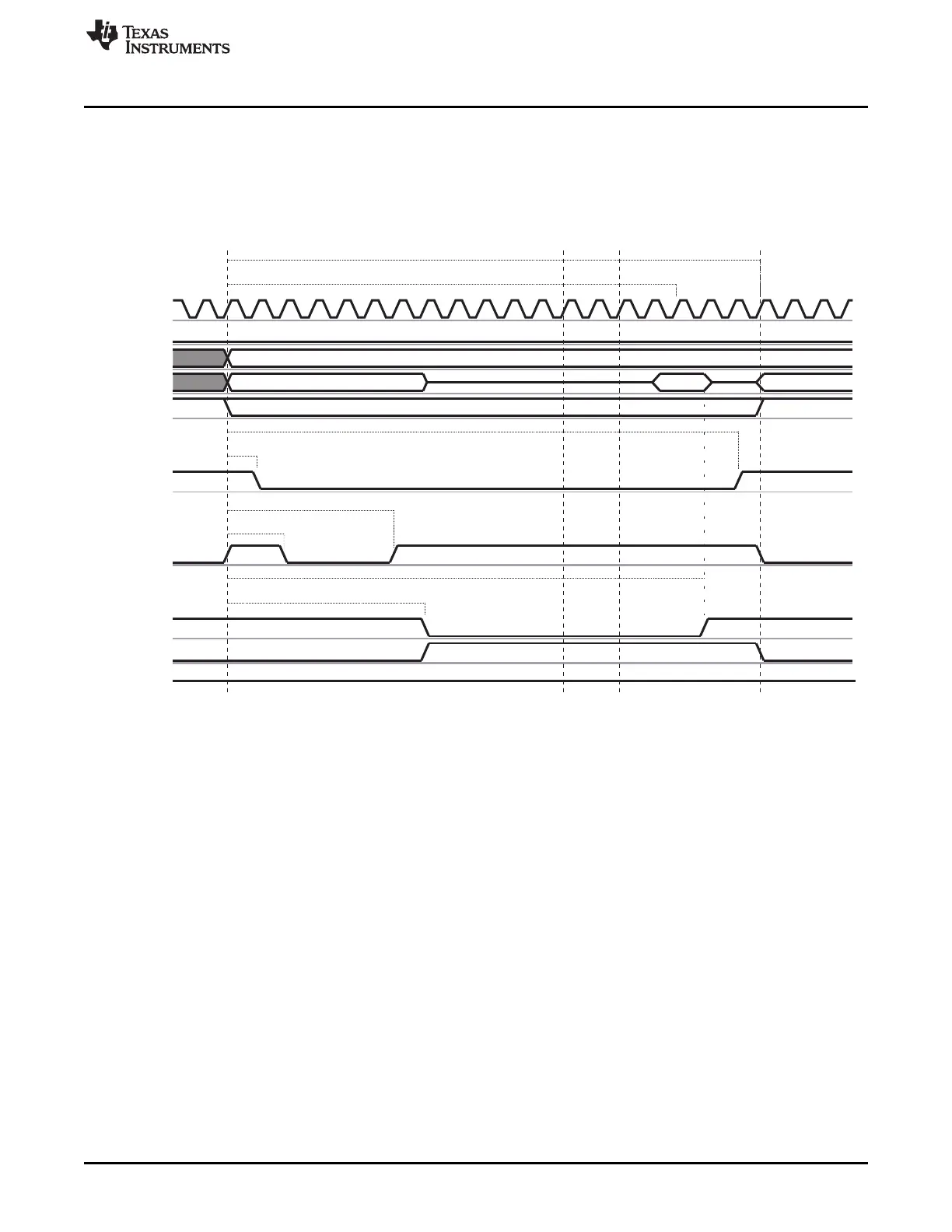

7.1.3.3.10.1.1 Access on Address/Data Multiplexed Devices

7.1.3.3.10.1.1.1 Asynchronous Single-Read Operation on an Address/Data Multiplexed Device

Figure 7-12 shows an asynchronous single read operation on an address/data-multiplexed device.

Figure 7-12. Asynchronous Single Read Operation on an Address/Data Multiplexed Device

7.1.3.3.10.1.1.2 Asynchronous Single Read on an Address/Data-Multiplexed Device

See Section 7.1.3.9.1 for formulas to calculate timing parameters.

Table 7-41 lists the timing bit fields to set up in order to configure the GPMC in asynchronous single read

mode.

When the GPMC generates a read access to an address/data-multiplexed device, it drives the address

bus until OEn assertion time. For details, see Section 7.1.3.3.8.2.3.

Address bits (A[16:1] from a GPMC perspective, A[15:0] from an external device perspective) are placed

on the address/data bus, and the remaining address bits GPMC_A[25:16] are placed on the address bus.

The address phase ends at OEn assertion, when the DIR signal goes from OUT to IN.

• Chip-select signal CSn

– CSn assertion time is controlled by the GPMC_CONFIG2_i[3-0] CSONTIME field. It controls the

address setup time to CSn assertion.

– CSn deassertion time is controlled by the GPMC_CONFIG2_i[12-8] CSRDOFFTIME field. It

controls the address hold time from CSn deassertion

• Address valid signal ADVn

– ADVn assertion time is controlled by the GPMC_CONFIG3_i[3-0] ADVONTIME field.

– ADVn deassertion time is controlled by the GPMC_CONFIG3_i[[12-8] ADVRDOFFTIME field.

281

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...