GPMC

www.ti.com

Any chip-select region can be qualified as a NAND region to constrain the ADVn_ALE signal as Address

Latch Enable (ALE active high, default state value at low) during address program access, and the

BE0n_CLE signal as Command Latch Enable (CLE active high, default state value at low) during

command program access. GPMC address lines are not used (the previous value is not changed) during

NAND access.

7.1.3.3.12.1.1 Chip-Select Configuration for NAND Interfacing in Byte or Word Stream Mode

The GPMC_CONFIG7_i register associated with a NAND device region interfaced in byte or word stream

mode can be initialized with a minimum size of 16 Mbytes, because any address location in the chip-select

memory region can be used to access a NAND data array. The NAND Flash protocol specifies an address

sequence where address bits are passed through the data bus in a series of write accesses with the ALE

pin asserted. After this address phase, all operations are streamed and the system requests address is

irrelevant.

To allow correct command, address, and data-access controls, the GPMC_CONFIG1_i register

associated with a NAND device region must be initialized in asynchronous read and write modes with the

parameters shown in Table 7-11. Failure to comply with these settings corrupts the NAND interface

protocol.

The GPMC_CONFIG1_i to GPMC_CONFIG4_i register associated with a NAND device region must be

initialized with the correct control-signal timing value according to the NAND device timing parameters.

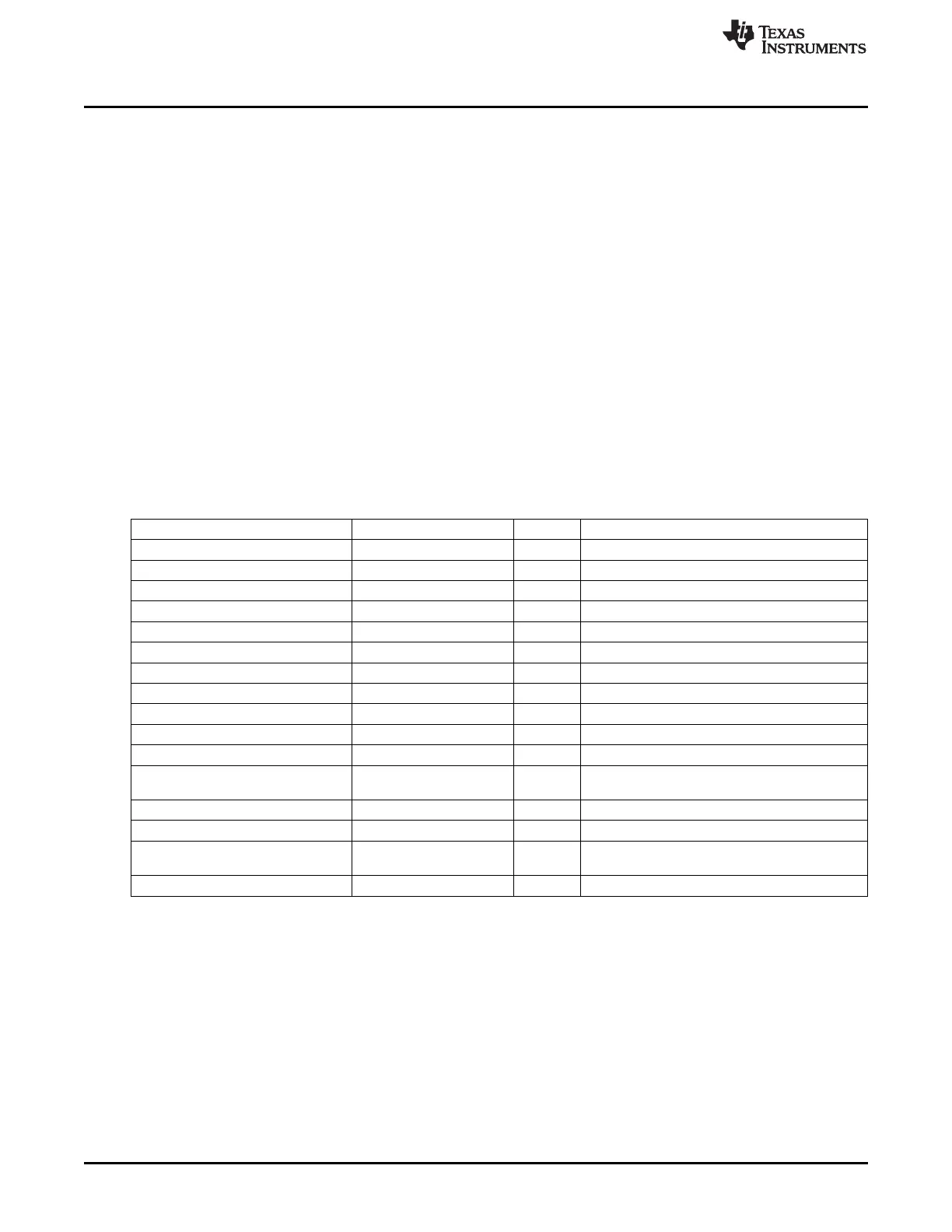

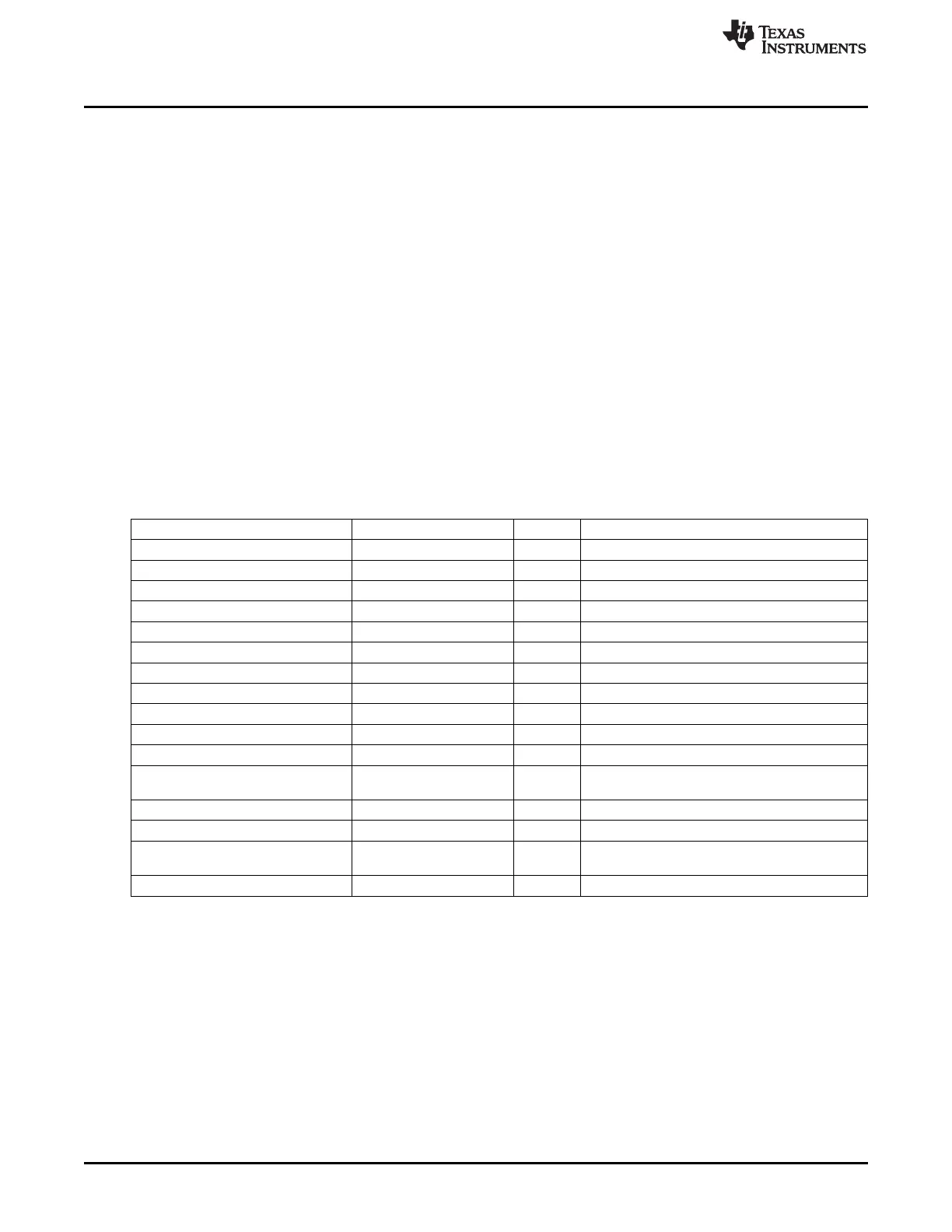

Table 7-11. Chip-Select Configuration for NAND Interfacing

Bit Field Register Value Comments

WRAPBURST GPMC_CONFIG1_i 0 No wrap

READMULTIPLE GPMC_CONFIG1_i 0 Single access

READTYPE GPMC_CONFIG1_i 0 Asynchronous mode

WRITEMULTIPLE GPMC_CONFIG1_i 0 Single access

WRITETYPE GPMC_CONFIG1_i 0 Asynchronous mode

CLKACTIVATIONTIME GPMC_CONFIG1_i 0b00

ATTACHEDDEVICEPAGELENGTH GPMC_CONFIG1_i Don't care Single-access mode

WAITREADMONITORING GPMC_CONFIG1_i 0 Wait not monitored by GPMC access engine

WAITWRITEMONITORING GPMC_CONFIG1_i 0 Wait not monitored by GPMC access engine

WAITMONITORINGTIME GPMC_CONFIG1_i Don't care Wait not monitored by GPMC access engine

WAITPINSELECT GPMC_CONFIG1_i Select which wait is monitored by edge detectors

DEVICESIZE GPMC_CONFIG1_i 0b00 or

8- or 16-bit interface

0b01

DEVICETYPE GPMC_CONFIG1_i 0b10 NAND device in stream mode

MUXADDDATA GPMC_CONFIG1_i 0b00 Nonmultiplexed mode

TIMEPARAGRANULARITY GPMC_CONFIG1_i 0 Timing achieved with best GPMC clock

granularity

GPMCFCLKDIVIDER GPMC_CONFIG1_i Don't care Asynchronous mode

7.1.3.3.12.1.2 NAND Device Command and Address Phase Control

NAND devices require multiple address programming phases. The MPU software driver is responsible for

issuing the correct number of command and address program accesses, according to the device

command set and the device address-mapping scheme.

NAND device-command and address-phase programming is achieved through write requests to the

GPMC_NAND_COMMAND_i and GPMC_NAND_ADDRESS_i register locations with the correct

command and address values. These locations are mapped in the associated chip-select register region.

The associated chip-select signal timing control must be programmed according to the NAND device

timing specification.

302

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...