GPMC

www.ti.com

7.1.3.3.12.3.2.2 Memory-Mapping of the BCH Codeword

BCH encoding considers a block of data to protect as a polynomial message M(x). In our standard case,

512 bytes of data (that is, 2 bits = 4096 bits) are seen as a polynomial of degree 2 - 1 = 4095, with

parameters ranging from M0 to M4095. For 512 bytes of data, 52 bits are required for 4-bit error

correction, and 104 bits are required for 8-bit error correction and 207 bits are required for 16-bit error

correction. The ECC is a remainder polynomial R(x) of degree 103 (or 51, depending on the selected

mode). The complete codeword C(x) is the concatenation of M(x) and R(x) as shown in Table 7-13.

Table 7-13. Flattened BCH Codeword Mapping (512 Bytes + 104 Bits)

Message M(x) ECC R(x)

Bit number M4095 ... M0 R103 ... R0

If the message is extended by the addition of spare bytes to be protected by the same ECC, the principle

is still valid. For example, a 3-byte extension of the message gives a polynomial message M(x) of degree

((512 + 3) × 8) - 1 = 4119, for a total of 3 + 13 = 16 spare bytes of spare, all protected as part of the same

codeword.

The message and the ECC bits are manipulated and mapped in the GPMC byte-oriented system. The

ECC bits are stored in:

• GPMC_BCH_RESULT0_i

• GPMC_BCH_RESULT1_i

• GPMC_BCH_RESULT2_i

• GPMC_BCH_RESULT3_i

7.1.3.3.12.3.2.3 Memory Mapping of the Data Message

The data message mapping shall follow the following rules:

• Bit endianness within a byte is little-endian, that is, the bytes LS bit is also the lowest-degree

polynomial parameter: a byte b7-b0 (with b0 the LS bit) represents a segment of polynomial b7 * x +

b6 * x + ... + b0 * x

• The message is mapped in the NAND starting with the highest-order parameters, that is, in the lowest

addresses of a NAND page.

• Byte endianness within the NANDs 16-bit words is big endian. This means that the same message

mapped in 8- and 16-bit memories has the same content at the same byte address.

The BCH module has no visibility over actual addresses. The most important point is the sequence of data

word the BCH sees. However, the NAND page is always scanned incrementally in read and write

accesses, and this produces the mapping patterns described in the following.

Table 7-14 and Table 7-15 show the mapping of the same 512-byte vector (typically a BCH message) in

the NAND memory space. Note that the byte 'address' is only an offset modulo 512 (200h), since the

same page may contain several contiguous 512-byte sectors (BCH blocks). The LSB and MSB are

respectively the bits M0 and M(2^12-1) of the codeword mapping given above. In both cases the data

vectors are aligned, that is, their boundaries coincide with the RAMs data word boundaries.

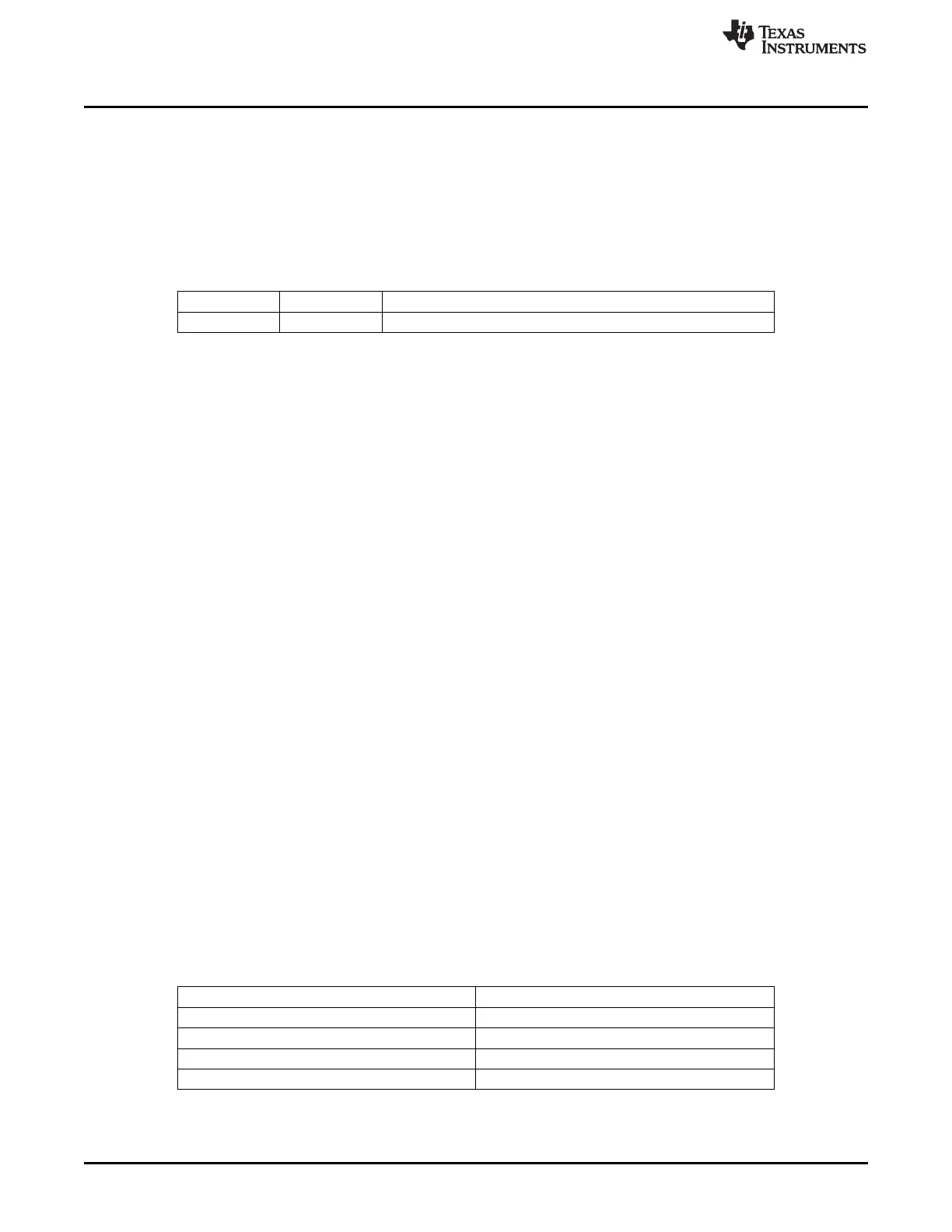

Table 7-14. Aligned Message Byte Mapping in 8-bit NAND

Byte Offset 8-Bit Word

0 (msb) Byte 511 (1FFh)

1h Byte 510 (1FEh)

⋮ ⋮

1FFh Byte 0 (0) (LSB)

316

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...