www.ti.com

GPMC

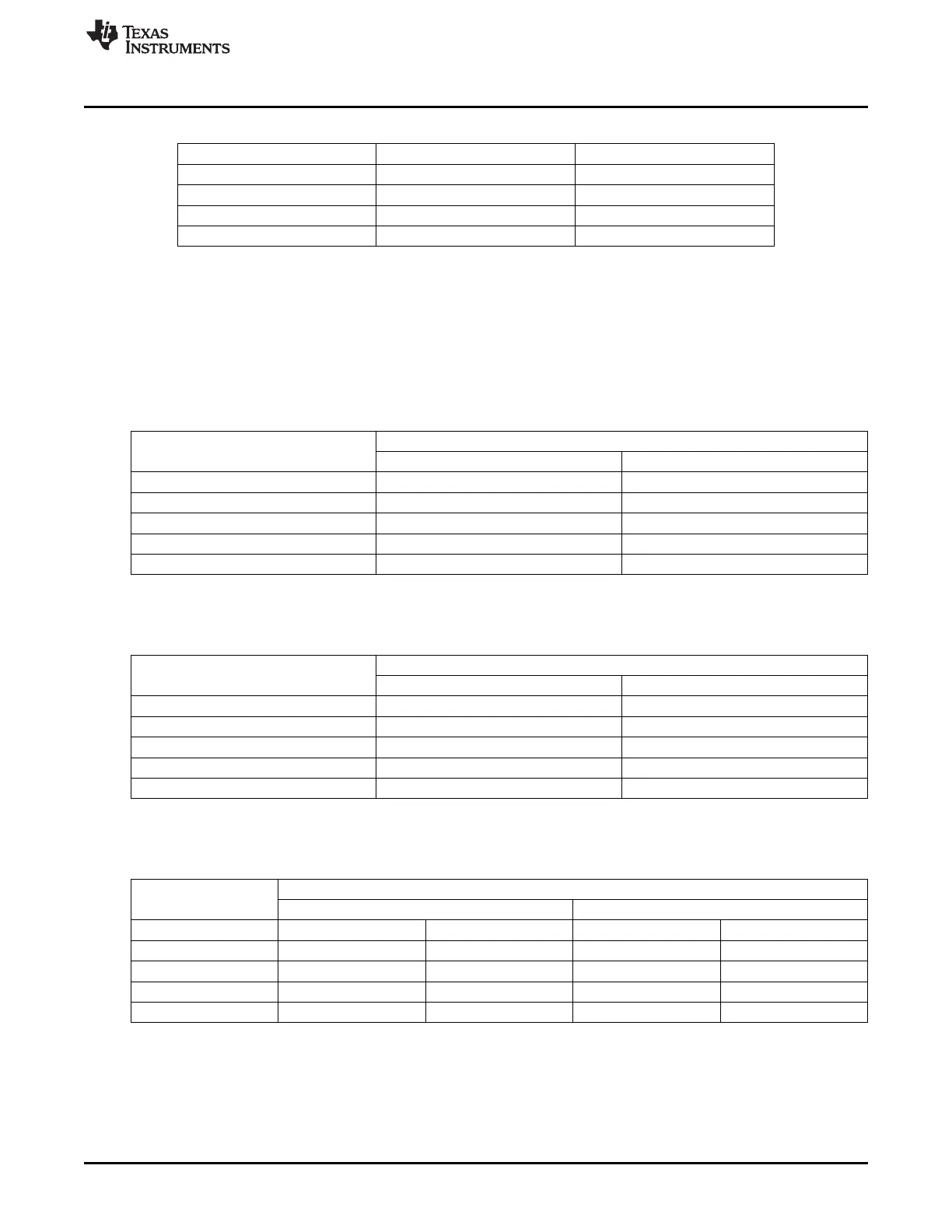

Table 7-15. Aligned Message Byte Mapping in 16-bit NAND

Byte Offset 16-Bit Words MSB 16-Bit Words LSB

0 Byte 510 (1FEh) (msb) Byte 511 (1FFh)

2h Byte 508 (1FCh) Byte 509 (1FDh)

⋮ ⋮ ⋮

1FEh Byte 0 (0) (lsb) Byte 1 (1)

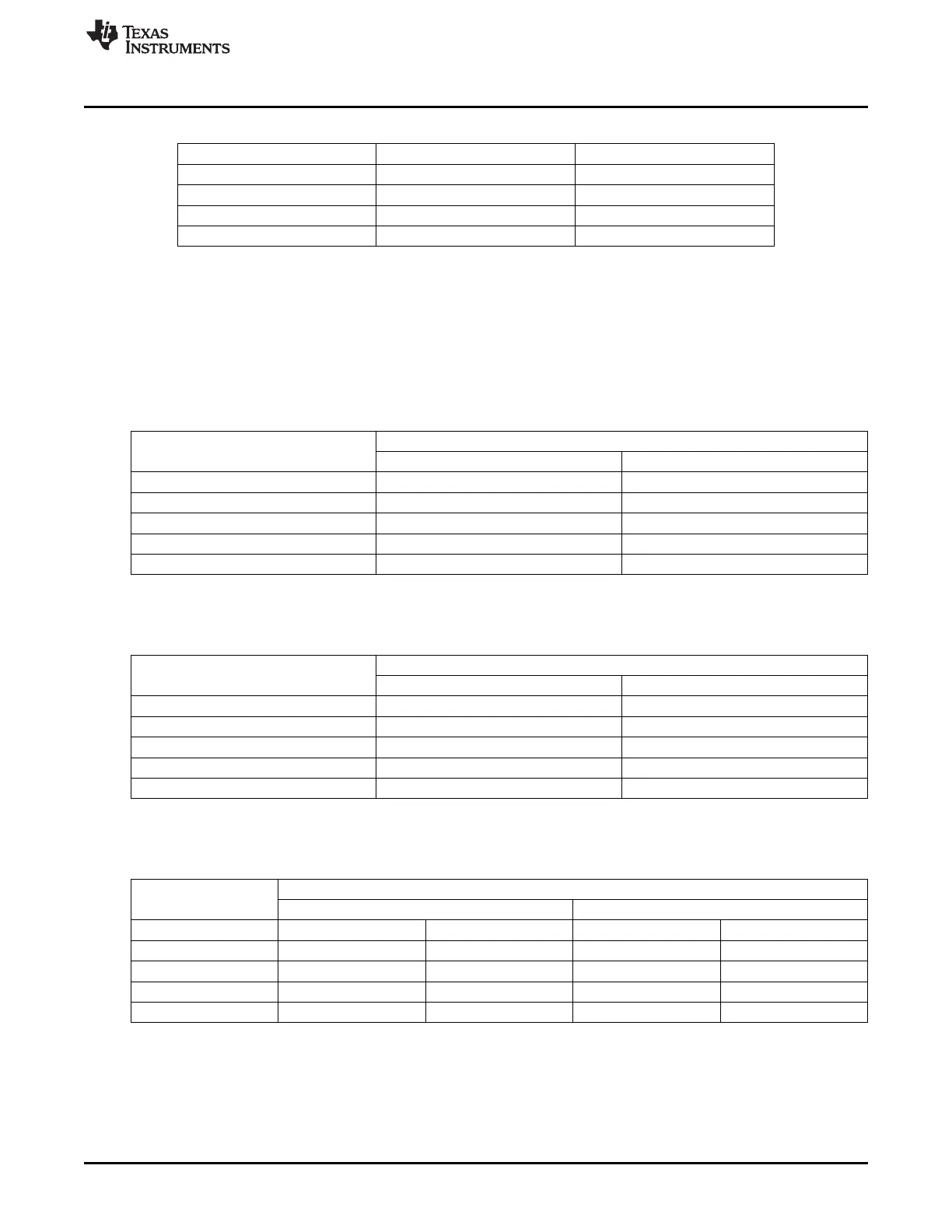

Table 7-16 and Table 7-17 show the mapping in memory of arbitrarily-sized messages, starting on access

(byte or 16-bit word) boundaries for more clarity. Note that message may actually start and stop on

arbitrary nibbles. A nibble is a 4-bit entity. The unused nibbles are not discarded, and they can still be

used by the BCH module, but as part of the next message section (for example, on another sectors ECC).

Table 7-16. Aligned Nibble Mapping of Message in 8-bit NAND

8-Bit Word

Byte Offset

4-Bit Most Significant Nibble 4-Bit Less Significant Nibble

1 (MSB) Nibble S-1 Nibble S-2

2 Nibble S-3 Nibble S-4

⋮ ⋮ ⋮

S/2 - 2 Nibble 3 Nibble 2

S/2 - 1 Nibble 1 Nibble 0 (LSB)

Table 7-17. Misaligned Nibble Mapping of Message in 8-bit NAND

8-Bit Word

Byte Offset

4-Bit Most Significant Nibble 4-Bit Less Significant Nibble

1 (MSB) Nibble S-1 Nibble S-2

2 Nibble S-3 Nibble S-4

⋮ ⋮ ⋮

(S+1)/2 - 2 Nibble 2 Nibble 1

(S+1)/2 - 1 Nibble 0 (LSB)

Table 7-18. Aligned Nibble Mapping of Message in 16-bit NAND

16-Bit Word

Byte Offset

4-Bit Most Significant Nibble 4-Bit Less Significant Nibble

0 Nibble S-3 Nibble S-4 (MSB) Nibble S-1 Nibble S-2

2 Nibble S-7 Nibble S-8 Nibble S-5 Nibble S-6

⋮ ⋮ ⋮ ⋮ ⋮

S/2 - 4 Nibble 5 Nibble 4 Nibble 7 Nibble 6

S/2 - 2 Nibble 1 Nibble 0 (LSB) Nibble 3 Nibble 2

317

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...