size1size1

size1size1

inactive

E E1 1U512 bytes 512 bytes

P E E512 bytes 512 bytes 1 1

U E E512 bytes 512 bytes

P E E512 bytes 512 bytes

11

size1

size1

10 i.

11

size1 size1size0

size0 size1 size1

size0 size1 size1

Data0 Data1 Unprotected (pooled) Ecc0 Ecc1

Pooled page spares

0 1 10inactiveRead 4 U E

Data0 Data1 Protected (pooled) Ecc0 Ecc1

Pooled page spares

0 1

0 1

0

1

inactive

0

Write

Read

7

3

P E

P E

Mode Size0 Size1

Mode Size0 Size1

Pooled spares

Spares covered by ECC0.

All ECC at the end (of page).

Pooled spares

Spares not covered by ECC.

All ECC at the end.

size0

Data0 Data1 Unprotected (pooled)

Pooled page spares

0 1 inactiveRead 9 U E

Mode Size0 Size1

Pooled spares

Spares not covered by ECC.

All ECC at the end, left-padded.

size0 size1 size1

size0 size1 size1

Data0 Data1 Protected (pooled) Ecc0 Ecc1

Pooled page spares

0 1

0 1

0

1

inactive

0

Write

Read

7

8

P 1+E

P E

Mode Size0 Size1

Pooled spares

Spares covered by ECC0.

All ECC at the end, left-padded.

Pad Pad

0i. i.

Ecc0 Ecc1Pad Pad

Sector data Sector data

Sector data Sector data

Sector data Sector data

Sector data Sector data

M5

M6

M7

M8

0 1Write 6 0

U/S

+1+E

inactive0 1Write 6 0

U/S

+E

www.ti.com

GPMC

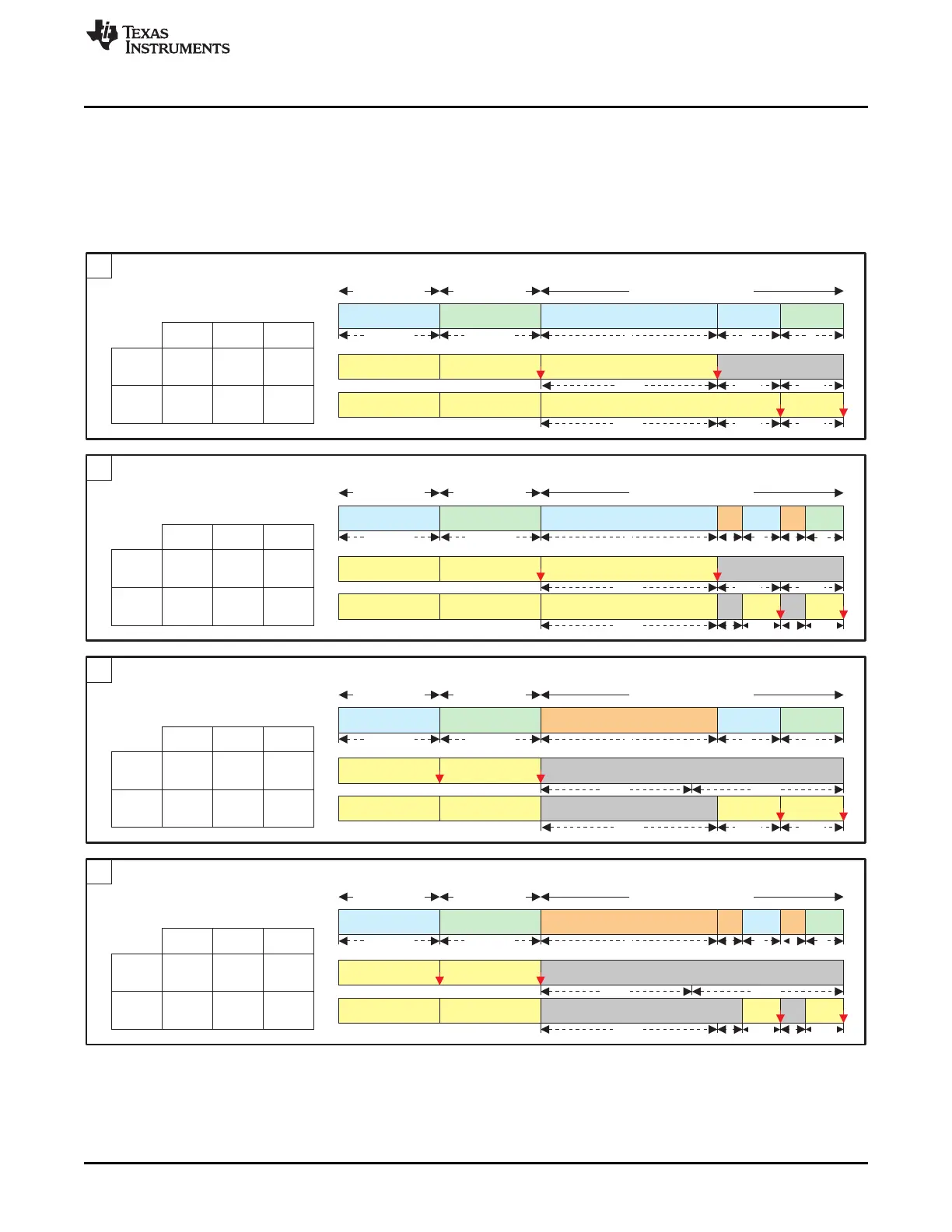

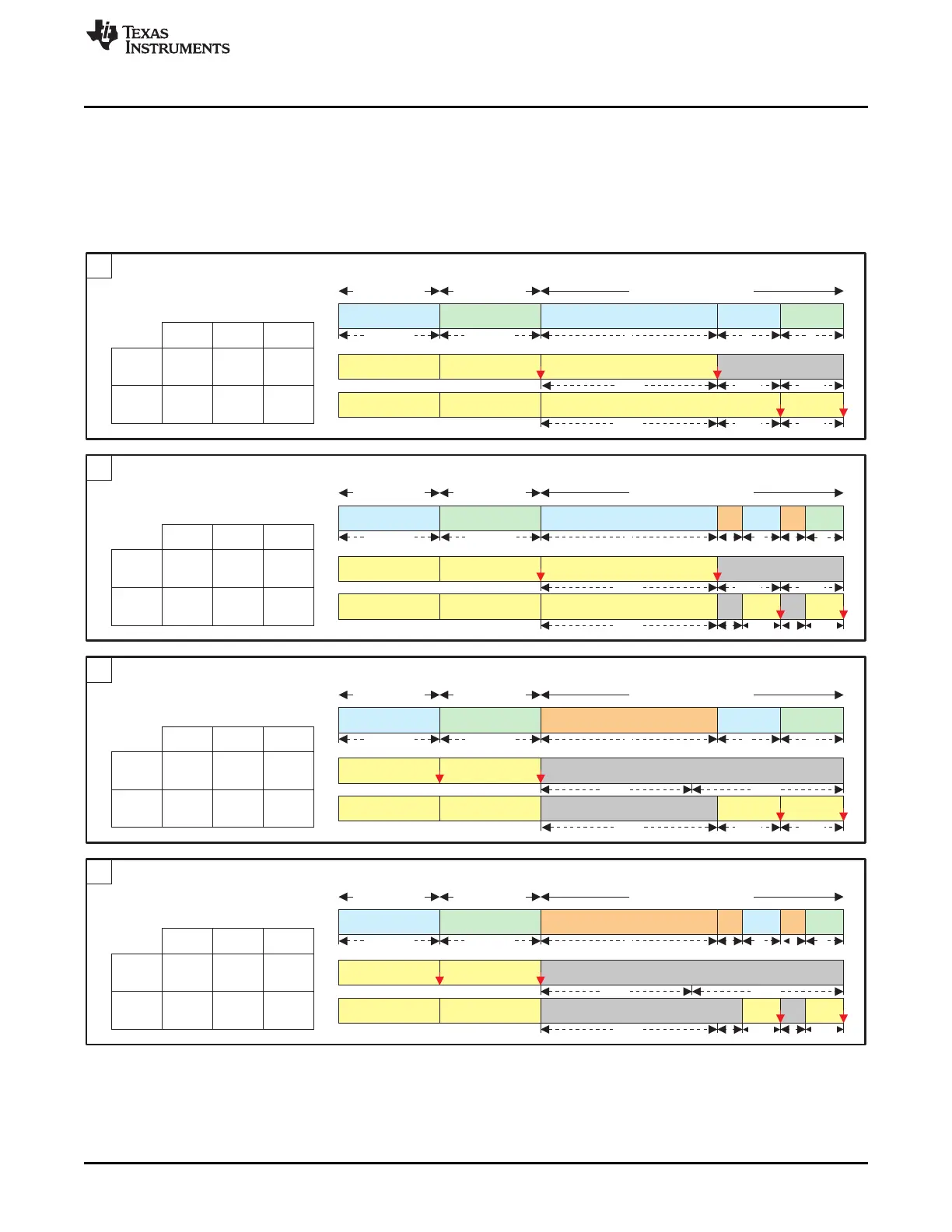

7.1.3.3.12.3.3.2 Pooled Spare Mapping

In these schemes (Figure 7-39), the spare area is pooled for the page.

• The ECC of each sector is aligned at the end of the spare area.

• The non-ECC spare data may or may not be covered by the ECC of sector 0

Figure 7-39. NAND Page Mapping and ECC: Pooled Spare Schemes

325

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...