GPMC_FCLK

GPMC_CLK

WAIT

Valid Address

Valid Address Data

CSONTIME

CSWROFFTIME

ADVONTIME

ADVWROFFTIME

WEONTIME

WRDATAONADMUXBUS

WEOFFTIME

WRCYCLETIME

nBE1/nBE0

nCS

nADV

nWE

A[27:17]

A[16:1]/D[15:0]

DIR

OUT

www.ti.com

GPMC

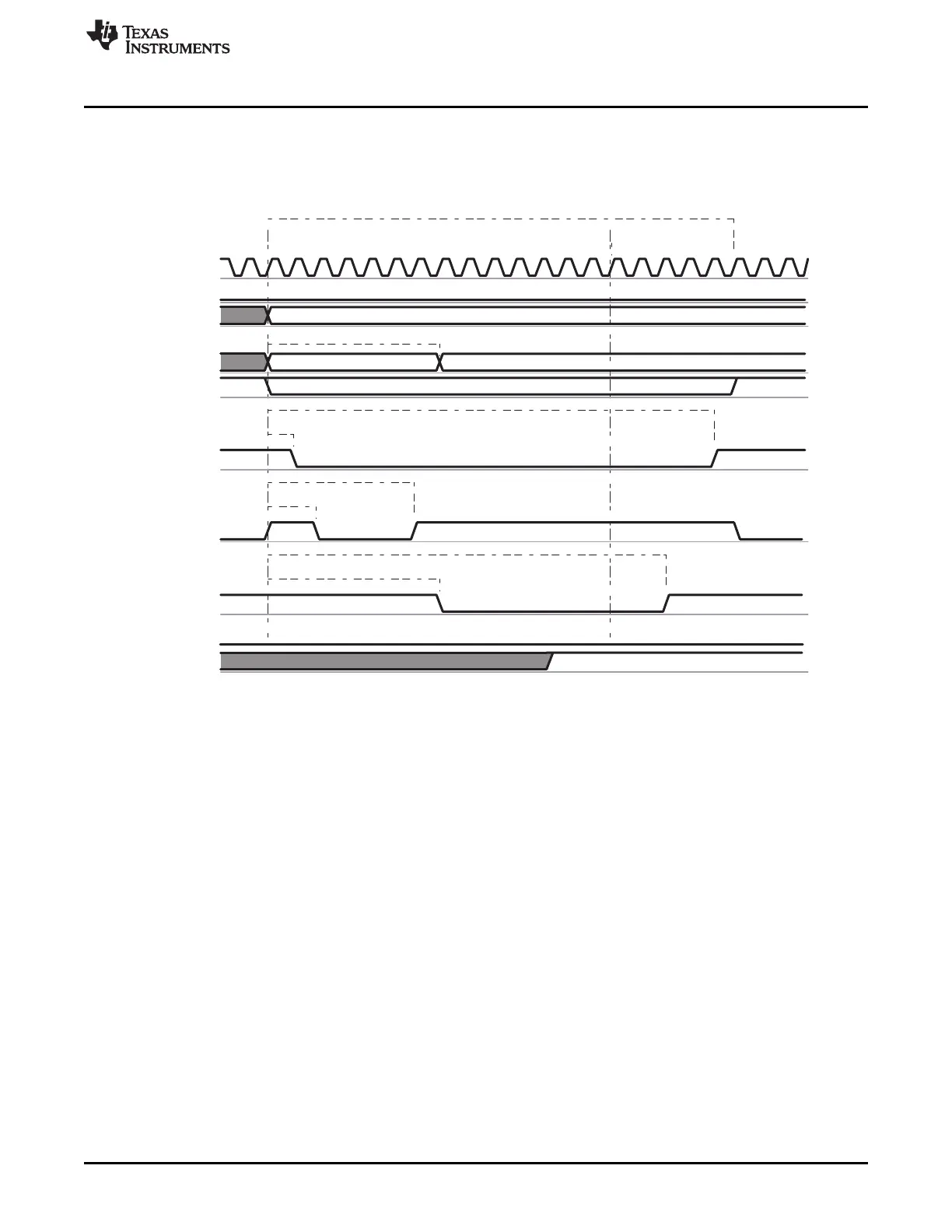

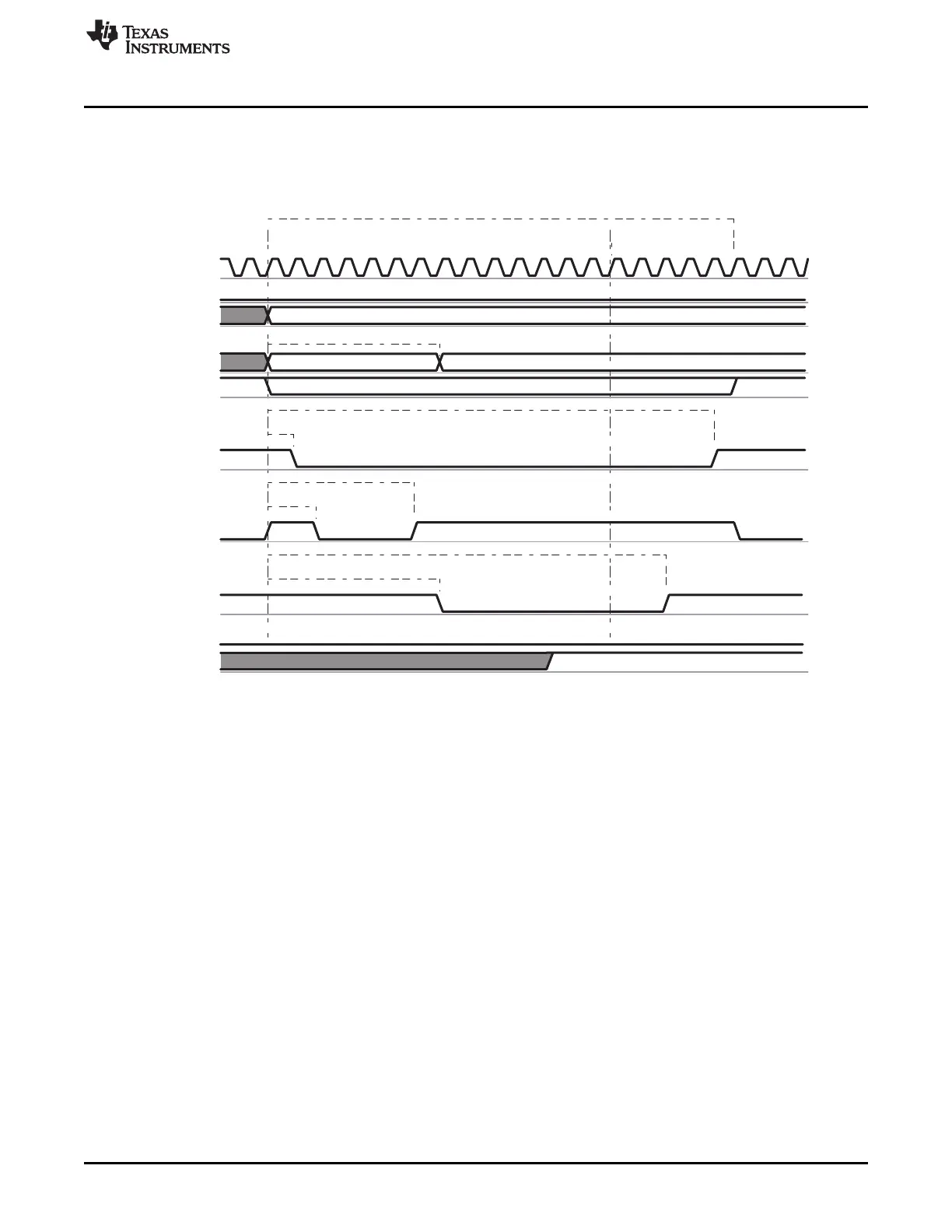

7.1.3.3.10.1.1.3 Asynchronous Single Write Operation on an Address/Data-Multiplexed Device

Figure 7-14 shows an asynchronous single write operation on an address/data-multiplexed device.

Figure 7-14. Asynchronous Single Write on an Address/Data-Multiplexed Device

7.1.3.3.10.1.1.4 Asynchronous Single Write on an Address/Data-Multiplexed Device

See Section 7.1.3.9.1 for formulas to calculate timing parameters.

Table 7-41 lists the timing bit fields to set up in order to configure the GPMC in asynchronous single write

mode. When the GPMC generates a write access to an address/data-multiplexed device, it drives the

address bus until WEn assertion time. For more information, see Section 7.1.3.3.8.2.3.

The CSn and ADVn signals are controlled in the same way as for asynchronous single read operation on

an address/data-multiplexed device.

• Write enable signal WEn

– WEn assertion indicates a write cycle.

– WEn assertion time is controlled by the GPMC_CONFIG4_i[19-16] WEONTIME field.

– WEn deassertion time is controlled by the GPMC_CONFIG4_i[28-24] WEOFFTIME field.

• Direction signal DIR: DIR signal is OUT during the entire access.

• The end of the access is defined by the GPMC_CONFIG5_i[12-8] WRCYCLETIME parameter.

Address bits A[16:1] (GPMC point of view) are placed on the address/data bus at the start of cycle time,

and the remaining address bits A[26:17] are placed on the address bus.

Data is driven on the address/data bus at a GPMC_CONFIG6_i[19-16] WRDATAONADMUXBUS time.

Write multiple access in asynchronous mode is not supported. If WRITEMULTIPLE is enabled with

WRITETYPE as asynchronous, the GPMC processes single asynchronous accesses.

283

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...