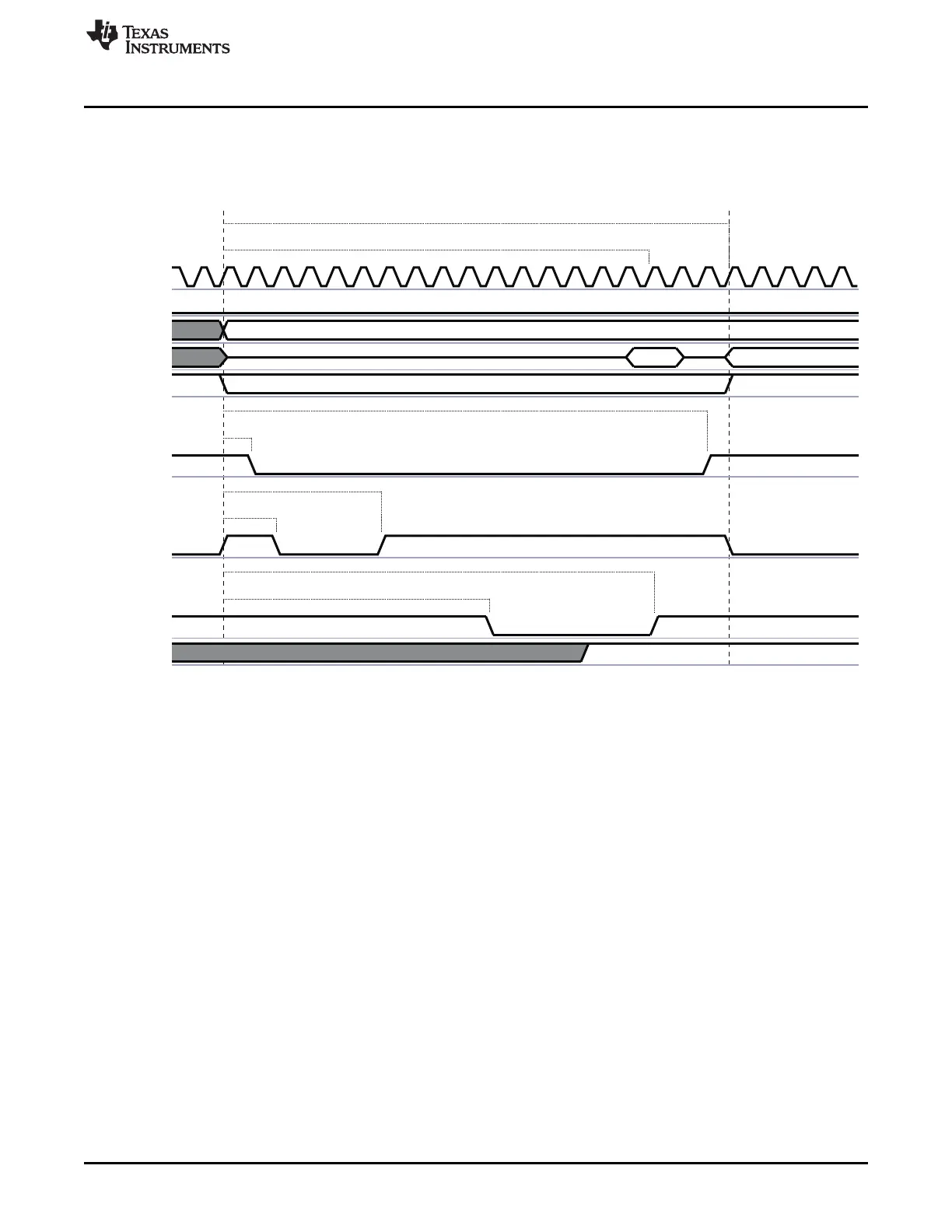

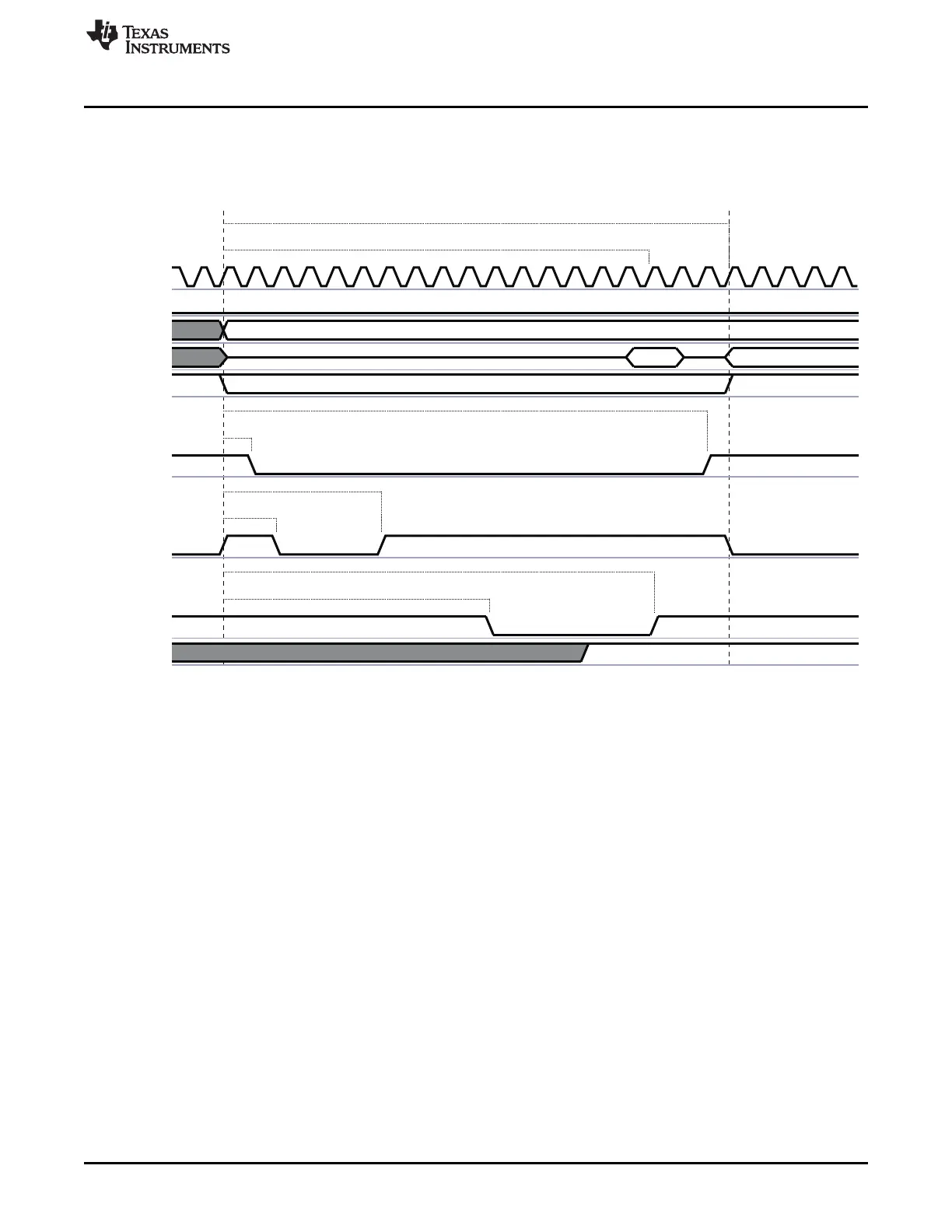

GPMC_FCLK

GPMC_CLK

WAIT

Valid Address

Data 0 Data 0

CSONTIME

CSRDOFFTIME

ADVONTIME

ADVRDOFFTIME

OEONTIME

OEOFFTIME

RDACCESSTIME

RDCYCLETIME

nBE1/nBE0

nCS

nADV

nOE

A[27:1]

D[15:0]

www.ti.com

GPMC

7.1.3.3.10.3.1 Asynchronous Single Read Operation on a Nonmultiplexed Device

Figure 7-24 shows an asynchronous single read operation on a nonmultiplexed device.

Figure 7-24. Asynchronous Single Read on an Address/Data-Nonmultiplexed Device

The 27-bit address is driven onto the address bus A[27:1] and the 16-bit data is driven onto the data bus

D[15:0].

Read data is latched at GPMC_CONFIG1_5[20-16] RDACCESSTIME completion time. The end of the

access is defined by the GPMC_CONFIG1_5[4-0] RDCYCLETIME parameter.

CSn, ADVn, OEn and DIR signals are controlled in the same way as address/data multiplexed accesses,

see Section 7.1.3.3.10.1.1.2.

297

SPRUH73H–October 2011–Revised April 2013 Memory Subsystem

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...