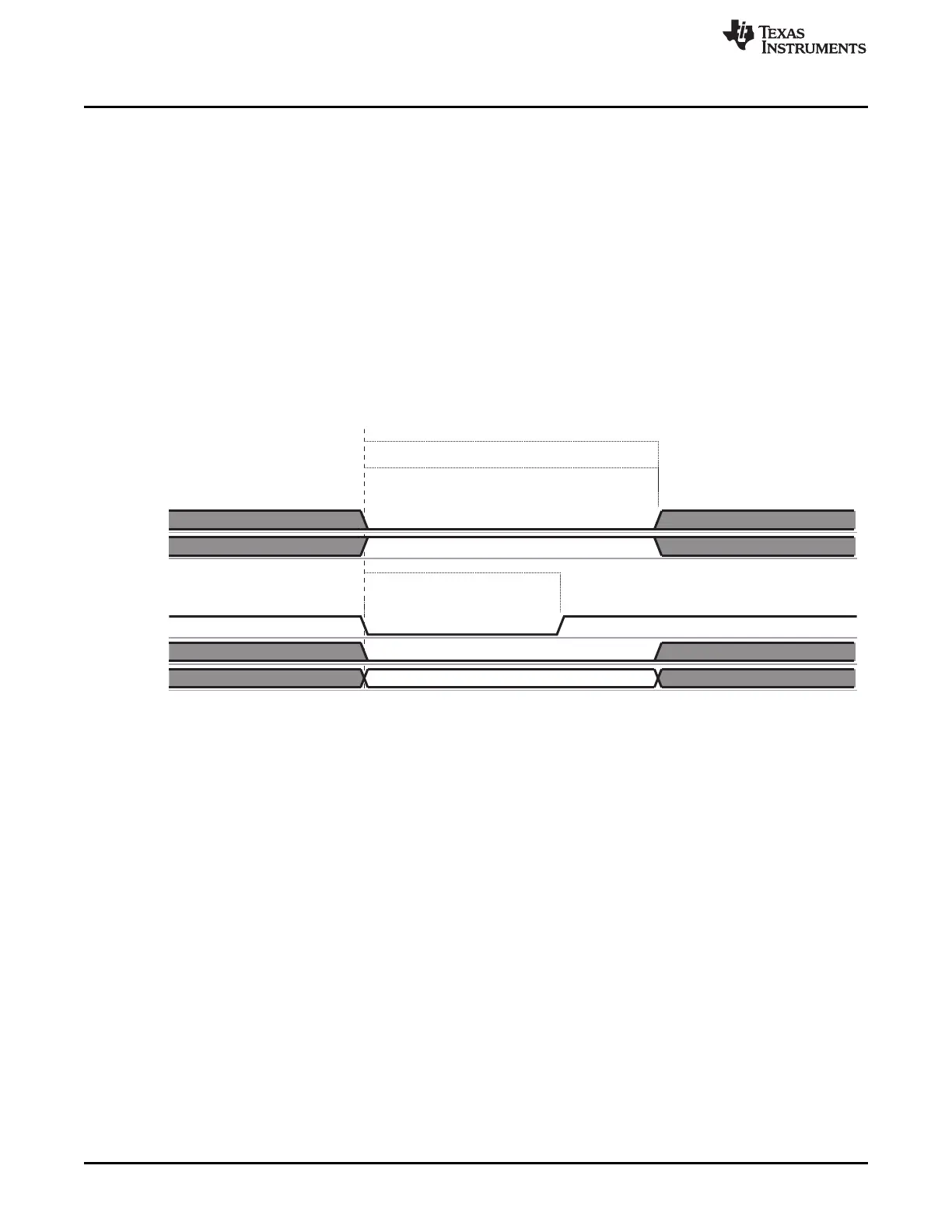

D[15:0]

Command

WEONTIME = 0

WEOFFTIME

CSWROFFTIME

WRCYCLETIME

CSONTIME = 0

nBE0/CLE

nCS

nWE

nADV/ALE

GPMC

www.ti.com

7.1.3.3.12.1.3 Command Latch Cycle

Writing data at the GPMC_NAND_COMMAND_i location places the data as the NAND command value on

the bus, using a regular asynchronous write access.

• CSn[i] is controlled by the CSONTIME and CSWROFFTIME timing parameters.

• CLE is controlled by the ADVONTIME and ADVWROFFTIME timing parameters.

• WE is controlled by the WEONTIME and WEOFFTIME timing parameters.

• ALE and REn (OEn) are maintained inactive.

Figure 7-27 shows the NAND command latch cycle.

CLE is shared with the BE0n output signal and has an inverted polarity from BE0n. The NAND qualifier

deals with this. During the asynchronous NAND data access cycle, BE0n (also BE1n) must not toggle,

because it is shared with CLE.

NAND Flash memories do not use byte enable signals at all.

Figure 7-27. NAND Command Latch Cycle

304

Memory Subsystem SPRUH73H–October 2011–Revised April 2013

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Loading...

Loading...